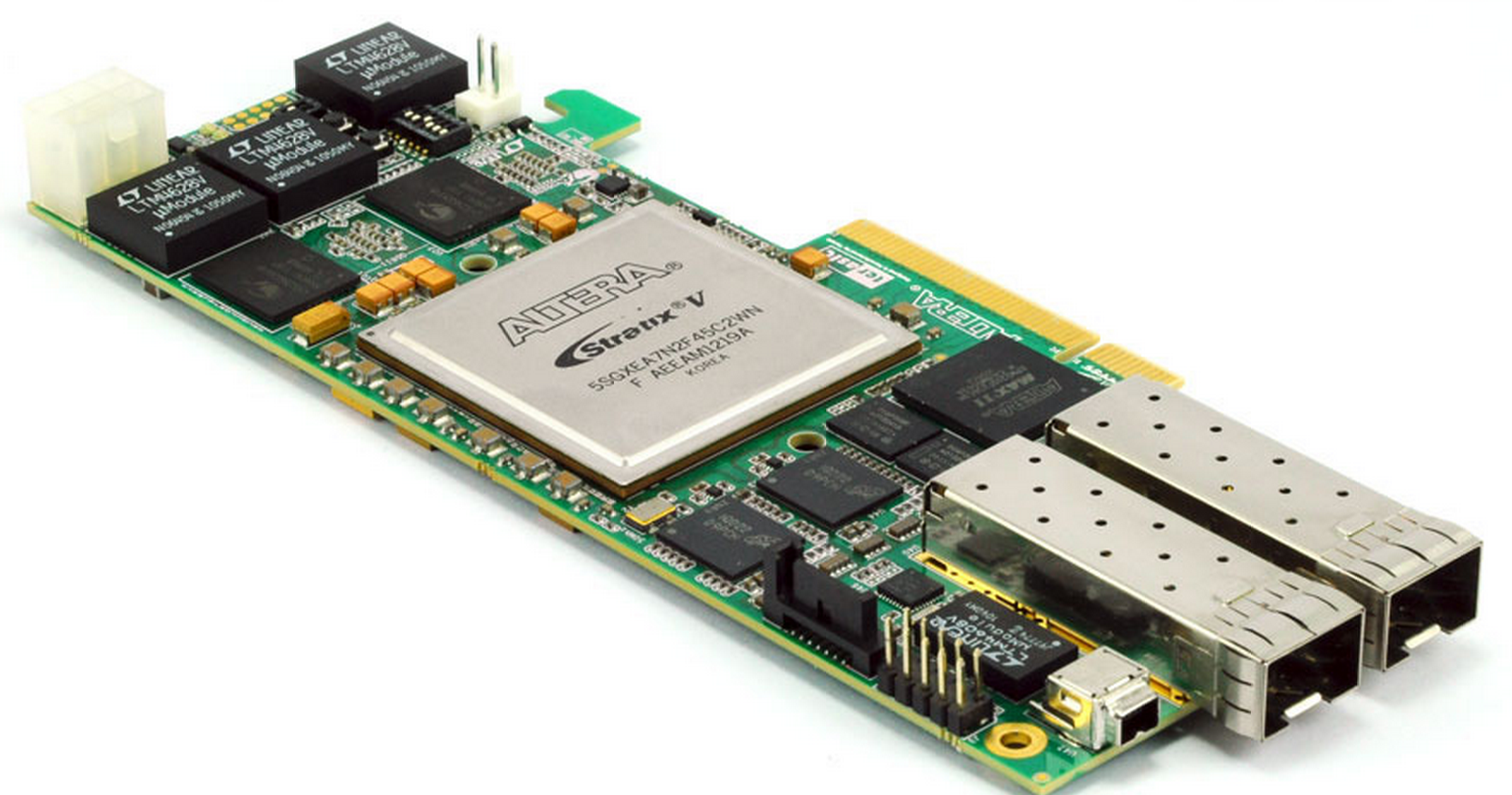

Terasic's Stratix V TR5-Lite FPGA Development Kit with X2Y® capacitors

Bypass Capacitor Characterization

These application notes explain how to measure capacitor parameters for different applications, and provide comparative performance metrics between X2Y and competing devices. Both raw-component and via-mounted data is shown, as well as inductance extraction methodology.

- Accurate Capacitor Inductance Extraction from s21 Measurements (6 pages, 156 Kb)

- Measurement and Comparative S21 Performance of Raw and Mounted Decoupling Capacitors (9 pages, 385 Kb)

- Comparative Device-Only Measurements of X2Y®, Arrays and Ordinary Capacitors (10 pages, 816 Kb)

- Ultra-Low Impedance Measurements Using 2-Port Measurements, ©2006 Agilent (52 pages, 2,440 Kb)

- Understanding Capacitor Inductance and Measurement in Bypass Applications (21 pages, 2,600 Kb)

- Bypass Capacitor Inductance, Data Sheet Simplicity to Practical Reality (17 pages, 501 Kb)

- Considerations for Capacitor Selection in FPGA Designs - received John Moynihan Award (best paper) for the 2005 Capacitor and Resistor Technology Symposium (CARTS) (7 pages, 398 Kb)

PCB Mounting Techniques for Bypass Capacitors

These papers explain how to optimize capacitor performance by minimizing inductance with proper capacitor mounting and PCB stack-up practices.

- Get the Most from X2Y Capacitors with Proper Attachment Techniques (8 pages, 631 Kb)

- X2Y® Inductance Ratings (3 pages, 233 Kb)

- Electromagnetic Analysis of Decoupling Capacitor Mounting Structures with Simbeor (32 pages, 9800 Kb)

- Impact of PCB Stack-up and Capacitor Via Design In Power Distribution Design, IEEE EMC Society SCV Meeting (37 pages, 4,520 Kb)

- X2Y® Capacitors in IC Back-Side Mounting Applications (12 pages, 962Kb)

High Performance Bypass Capacitor Application Design Methods and Examples

These papers demonstrate power supply bypass design techniques, provide a Bypass Network Synthesis Procedure, and show real world performance examples using X2Y® capacitors.

- X2Y® In DRAM Applications (17 pages, 1000KB)

- PCB Power Delivery Optimizations for the Cost Driven Era (Manuscript) (16 pages, 639kb)

- PCB Power Delivery Optimizations for the Cost Driven Era (Presentation) (16 pages, 926kb)

- X2Y® FPGA SerDes Bypass (123 pages, 1931kb)

- Analysis, Speeding Edge “Current Source”Article by John Zasio Vol. 1, Issue 4 (8 pages, 514 kbs)

- Power Delivery Network (PDN) Tool User Guide, ©2009 Altera Corporation

- High Performance FPGA Bypass Filter Networks, DesignCon 2005 (Bypass Network Synthesis Procedure on pg. 18) (20 pages, 2,851 Kb)

- Does position matter? Locating bypass capacitors for effective power distribution and EMC control, IEEE EMC Society SCV Meeting (30 pages, 1,210 Kb)

- Impact of PCB Stack-up and Capacitor Via Design In Power Distribution Design, IEEE EMC Society SCV Meeting (37 pages, 4,520 Kb)

- Application of X2Y Capacitors in Power Delivery Networks, IEEE EMC Society, RTP Chapter Meeting (40 pages, 7.96 Mb)

- Using a Spatial View to Understand and Solve Common Power Bypass Problems, IEEE EMC Society, SVC Chapter Meeting (27 pages, 1.05 Mb)

- Bypass Filter Design Considerations for Modern Digital Systems, A Comparative Evaluation of the Big “V”, Multi-pole, and Many Pole Bypass Strategies, DesignCon 2006 (23 pages, 1,843 Kb)

- Low-power, high-intercept interface to the ADS5424 14-bit, 105-MSPS converter for undersampling applications, Texas Instruments Incorporated (performance example) (10 pages, 489 Kb)

- X2Y Live FPGA Power Bypass, details FPGA design used in the video; "Low Inductance Capacitors Packages" (performance example) (21pages, 1,376 Kb)

- X2Y® vs. Feedthroughs in Digital Bypass Applications

- X2Y® Capacitor Plus Diode Kick-start

X2Y® Spice Model/Simulation Options

These links and papers are sources of SPICE models for X2Y® components and design tools that incorporate an X2Y® component library within the tool for circuit design analysis.

Component Model

The links below lead to downloadable zip files of the X2Y® HSPICE models for PC and UNIX and iSPICE models for PC from our various manufacturers. An equivalent circuit file for the models is also provided.

- X2Y® Equivalent Circuit for Models (zip, 67Kb)

- X2Y® HSPICE Component Library for PC (zip, 7Kb)

- X2Y® HSPICE Component Library for UNIX (2 pages, 28Kb)

- X2Y® iSPICE Component Library for PC (3 pages, 9Kb)

Component Model

Cadence Allegro® PCB PI OPTION, Release 15.7, Cadence® Allegro® PCB SI provides an integrated high-speed design and analysis environment for engineers creating complex digital PCB systems. Allegro® PCB PI option provides power integrity design and analysis at all frequency ranges of interest.

- X2Y® Components Library for Cadence Allegro® PCB PI option (Johanson Components) (zip, 4Kb)

- X2Y® Components Library for Cadence Allegro® PCB PI option (Yageo Components) (zip, 4Kb)

- Measurement Overview for X2Y® Component Library (3 pages, 224Kb)

- Installation Manual (2 pages, 28Kb)

DESIGN TOOL

PI Advisor™, an optional tool for ANSYS SIWAVE™, is a full-wave electromagnetic field solver that automatically optimizes power distribution systems. ANSYS SIWAVE™ now provides a library of low-inductance X2Y® capacitors for simulation analysis in product designs

- ANSYS SIWAVE™ brochure

DESIGN TOOL

Altera’s Power Distribution Network (PDN) Design Tool is a graphical tool used with Altera® FPGAs to optimize the board-level PDN. The tool incorporates a library of low-inductance X2Y® capacitors and an “X2Y_Mount” tab to optimize mounting inductance. Altera’s AN 574 appnote describes PDN design methodology in detail.

- Power Delivery Network (PDN) Tool (zip file contains excel tool)

- Power Delivery Network (PDN) Tool User Guide.